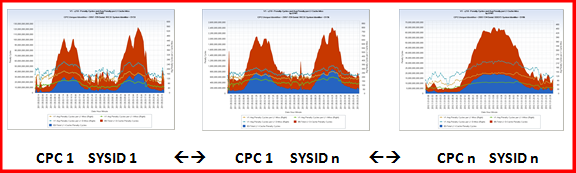

Workload Hint (Low-1 Avg-2 High-3)

CML1RNI – V1 Relative Nest Intensity

CMLPCL1M – Pct Level 1 Cache Miss

Workload Hint Reference Area – shaded gray from 1-3

DATEHHMM – Date: Hour : Minute

CML1PC15 – V1 PCT L1 from L1.5

CML1PC2A – V1 PCT L1 from L2 On-Bk

CML1PC2B – V1 PCT L1 from L2 Off-Bk

CML1PC3A – V1 PCT L1 from Local Memory

CML1PC3B – V1 PCT L1 from Remote Memory

AVGPCBSY – Avg IPU Busy for LPAR

CMLPCL1M – Pct Level 1 Cache Miss

DATEHHMM – Date: Hour : Minute

CML1PD15 – V1 PCT L1-D from L1.5

CML1PD2A – V1 PCT L1-D from L2 On-Bk

CML1PD2B – V1 PCT L1-D from L2 Off-Bk

CML1PD3A – V1 PCT L1-D from Local Memory

CML1PD3B – V1 PCT L1-D from Remote Memory

AVGPCBSY – Avg IPU Busy for LPAR

CMLPCL1M – Pct Level 1 Cache Miss

DATEHHMM – Date: Hour : Minute

CML1PI15 – V1 PCT L1-I from L1.5

CML1PI2A – V1 PCT L1-I from L2 On-Bk

CML1PI2B – V1 PCT L1-I from L2 Off-Bk

CML1PI3A – V1 PCT L1-I from Local Memory

CML1PI3B – V1 PCT L1-I from Remote Memory

AVGPCBSY – Avg IPU Busy for LPAR

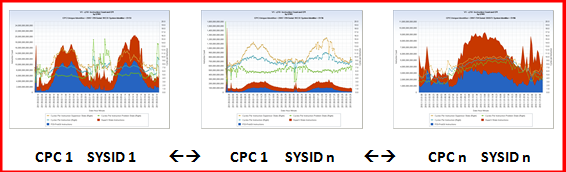

CMLPCL1M – Pct Level 1 Cache Miss

DATEHHMM – Date: Hour : Minute

CMLB3 – Total L1 I-Cache Penalty Cycles

CMLB5 – Total L1 D-Cache Penalty Cycles

CML1AVPM – V1 Avg Penalty Cycles per L1 Miss

CML1AVPD – V1 Avg Penalty Cycles per L1 D-Miss

CML1AVPI – V1 Avg Penalty Cycles per L1 I-Miss

DATEHHMM – Date: Hour : Minute

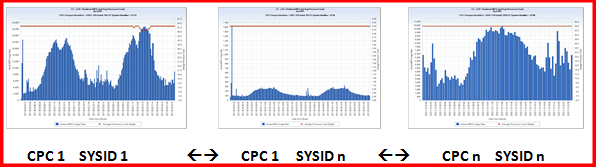

CMLMIPS – Actual MIPS Usage Rate

CMLAVIPU – Average Processor Count

DATEHHMM – Date: Hour : Minute

CMLP33 – P33-ProbSt Instructions

CMLS33 – SuperV-State Instructions

CMLCPI – Cycles per Instrucion

CPI_P – Cycles per Instruction Problem State

CPI_S – Cycles per Instruction Supervisor State

DATEHHMM – Date: Hour : Minute

|

Copyright © 2014 CA.

All rights reserved.

|

|