A design objective of IBM mainframe CPC’s is that when an instruction or datum is fetched from the IPU level 1 cache, the retrieval completes in a single machine cycle. With the introduction of the IBM z10 CPC, the CPC cycle rate increased dramatically from the 1.7 GHz rate of the previous z/9 CPC to 4.4 GHz. At this significantly higher cycle rate, the Level 1 data and instruction caches had to be reduced in size to continue to meet the one cycle retrieval objective.

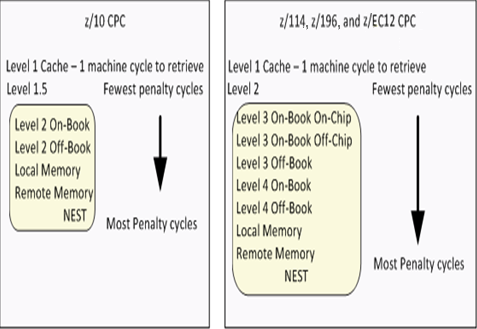

Beginning with the z10, and continuing with the z196 (5.2 GHz), and zEC12 (5.5 GHz), to maximize CPC performance, IBM introduced additional layers of cache between the Level 1 cache and real memory. The number of machine cycles required to retrieve an item from these intermediate cache levels increases from level to level, with the worst performance occurring when the item must be retrieved from remote memory, where it can take several hundred machine cycles for retrieval. The machine cycles expended while attempting to find and retrieve a required datum or instruction are referred to as penalty cycles:

When preparing to add additional capacity to a z10 or later generation CPC, or to upgrade to a newer generation CPC, it is essential to understand the cache use characteristics of the workloads running on your z/OS LPARs in order to understand how much capacity is required to meet your performance objectives. LPARs whose workloads experience high rates of Level 1 cache misses for data and instructions will experience high numbers of penalty cycles. If the required items are frequently found in the deeper levels of cache or real memory, an area referred to as the “nest”, the number of penalty cycles increases. The IBM metric Relative Nest Intensity (RNI) provides a means to quantify this behavior. Higher RNI values mean greater access of the “nest” when retrieving required items not found in the Level 1 cache.

High numbers of penalty cycles incurred by LPAR workloads effectively degrade CPC capacity. When adding additional IPUs to a z10 or later generation CPC, you must be aware of the Level 1 cache miss percentages and RNI values to understand how much capacity is actually realized with the additional engines. Similarly, when upgrading from a z10 or later generation CPC, the cache and memory use characteristics of your LPAR workloads must be understood to accurately configure the new CPC.

These charts can also be used to validate improved Level 1 cache hit percentages when activating an IBM option such as HIPERDISPATCH, where the objective is to direct specific LPAR logical engines to be repeatedly dispatched on the same physical engine, so that needed data and instructions are found in the low-level caches.

Finally, these charts can be used to identify LPARs whose workloads incur abnormally high numbers of penalty cycles. Application upgrades, designed to improve data and instruction Level 1 cache hit percentages and to reduce penalty cycles, can be evaluated using this query. Because the data processed by this query is LPAR level, in order to evaluate individual application behavior you may need to set up controlled environments where specific applications are executed in relative isolation at specific times.

|

Copyright © 2014 CA.

All rights reserved.

|

|